- Easily Interfaced to Microprocessors

- On-Chip Data Latches

- Monotonic Over the Entire A/D Conversion Range

- Segmented High-Order Bits Ensure Low-Glitch Output

- Interchangeable With Analog Devices AD7524, PMI PM-7524, and Micro Power Systems MP7524

- Fast Control Signaling for Digital Signal-Processor Applications Including Interface With TMS320

- CMOS Technology

| KEY PERFORMANCE SPECIFICATIONS             |             |  |  |  |  |

|--------------------------------------------|-------------|--|--|--|--|

| Resolution                                 | 8 Bits      |  |  |  |  |

| Linearity error                            | 1/2 LSB Max |  |  |  |  |

| Power dissipation at V <sub>DD</sub> = 5 V | 5 mW Max    |  |  |  |  |

| Setting time                               | 100 ns Max  |  |  |  |  |

| Propagation delay time                     | 80 ns Max   |  |  |  |  |

### description

The TLC7524C, TLC7524E, and TLC7524I are CMOS, 8-bit, digital-to-analog converters (DACs) designed for easy interface to most popular microprocessors.

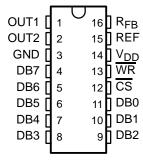

### D OR N PACKAGE (TOP VIEW)

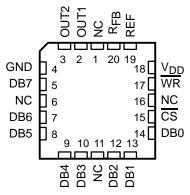

# FN PACKAGE (TOP VIEW)

NC-No internal connection

The devices are 8-bit, multiplying DACs with input latches and load cycles similar to the write cycles of a random access memory. Segmenting the high-order bits minimizes glitches during changes in the most significant bits, which produce the highest glitch impulse. The devices provide accuracy to 1/2 LSB without the need for thin-film resistors or laser trimming, while dissipating less than 5 mW typically.

Featuring operation from a 5-V to 15-V single supply, these devices interface easily to most microprocessor buses or output ports. The 2- or 4-quadrant multiplying makes these devices an ideal choice for many microprocessor-controlled gain-setting and signal-control applications.

The TLC7524C is characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C. The TLC7524I is characterized for operation from  $-25^{\circ}$ C to  $85^{\circ}$ C. The TLC7524E is characterized for operation from  $-40^{\circ}$ C to  $85^{\circ}$ C.

#### **AVAILABLE OPTIONS**

|               |                                     | PACKAGE                         |                    |

|---------------|-------------------------------------|---------------------------------|--------------------|

| TA            | SMALL OUTLINE<br>PLASTIC DIP<br>(D) | PLASTIC CHIP<br>CARRIER<br>(FN) | PLASTIC DIP<br>(N) |

| 0°C to 70°C   | TLC7524CD                           | TLC7524CFN                      | TLC7524CN          |

| -25°C to 85°C | TLC7524ID                           | TLC7524IFN                      | TLC7524IN          |

| -40°C to 85°C | TLC7524ED                           | TLC7524EFN                      | TLC7524EN          |

SLAS061A - SEPTEMBER 1986 - REVISED MARCH 1995

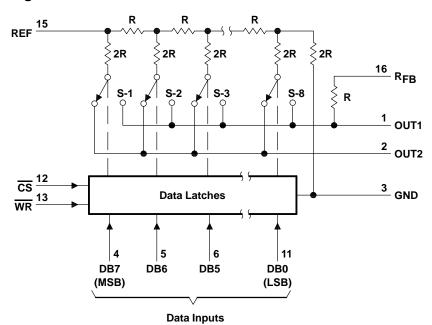

### functional block diagram

Terminal numbers shown are for the D or N package.

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>DD</sub>                  |                                       | -0.3 V to 16.5 V                           |

|--------------------------------------------------------|---------------------------------------|--------------------------------------------|

|                                                        |                                       |                                            |

| Digital input voltage range, V <sub>I</sub>            |                                       | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Reference voltage, V <sub>ref</sub>                    |                                       | ±25 V                                      |

| Peak digital input current, I <sub>1</sub>             |                                       | 10 μΑ                                      |

| Operating free-air temperature range, T <sub>A</sub> : | TLC7524C                              | 0°C to 70°C                                |

|                                                        | TLC7524I                              | −25°C to 85°C                              |

|                                                        | TLC7524E                              | −40°C to 85°C                              |

| Storage temperature range, T <sub>sta</sub>            |                                       | −65°C to 150°C                             |

| Case temperature for 10 seconds, T <sub>C</sub> : FN   |                                       |                                            |

| Lead temperature 1.6 mm (1/16 inch) from               | n case for 10 seconds: D or N package |                                            |

# TLC7524C, TLC7524E, TLC7524I 8-BIT MULTIPLYING DIGITAL-TO-ANALOG CONVERTERS

SLAS061A - SEPTEMBER 1986 - REVISED MARCH 1995

### recommended operating conditions

|                                              |          | $V_{DD} = 5 V$ $V_{DD} = 15 V$ |      |     | V <sub>DD</sub> = 5 V |      | ٧   | UNIT |      |  |

|----------------------------------------------|----------|--------------------------------|------|-----|-----------------------|------|-----|------|------|--|

|                                              |          |                                | MIN  | NOM | MAX                   | MIN  | NOM | MAX  | UNII |  |

| Supply voltage, V <sub>DD</sub>              |          |                                | 4.75 | 5   | 5.25                  | 14.5 | 15  | 15.5 | V    |  |

| Reference voltage, V <sub>ref</sub>          |          |                                |      | ±10 |                       |      | ±10 |      | V    |  |

| High-level input voltage, VIH                |          |                                | 2.4  |     |                       |      |     |      | V    |  |

| Low-level input voltage, V <sub>IL</sub>     |          |                                |      |     | 8.0                   |      |     | 1.5  | V    |  |

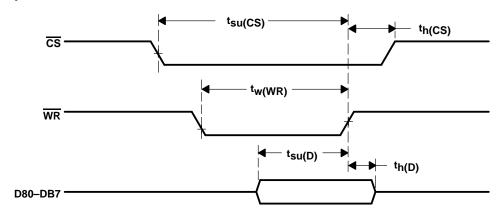

| CS setup time, t <sub>SU(CS)</sub>           |          |                                | 40   |     |                       | 40   |     |      | ns   |  |

| CS hold time th(CS)                          |          |                                | 0    |     |                       | 0    |     |      | ns   |  |

| Data bus input setup time t <sub>su(D)</sub> |          |                                | 25   |     |                       | 25   |     |      | ns   |  |

| Data bus input hold time th(D)               |          |                                | 10   |     |                       | 10   |     |      | ns   |  |

| Pulse duration, WR low, t <sub>W(WR)</sub>   |          |                                | 40   |     |                       | 40   |     |      | ns   |  |

|                                              | TLC7524C |                                | 0    |     | 70                    | 0    |     | 70   |      |  |

| Operating free-air temperature, TA           | TLC7524I |                                | -25  |     | 85                    | -25  |     | 85   | °C   |  |

|                                              | TLC7524E |                                | -40  |     | 85                    | -40  |     | 85   |      |  |

# electrical characteristics over recommended operating free-air temperature range, $V_{ref}$ = $\pm 10$ V, OUT1 and OUT2 at GND (unless otherwise noted)

|                 | PARAMETER                                               |           | TEST CONDITIONS                                                                              | V <sub>DD</sub> = 5 V |      | V <sub>DD</sub> = 15 V |     |       | UNIT |        |

|-----------------|---------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------|-----------------------|------|------------------------|-----|-------|------|--------|

|                 | PARAMETER                                               |           | TEST CONDITIONS                                                                              |                       | TYP  | MAX                    | MIN | TYP   | MAX  | UNIT   |

| lіН             | High-level input curi                                   | ent       | $V_I = V_{DD}$                                                                               |                       |      | 10                     |     |       | 10   | μΑ     |

| IլL             | Low-level input curr                                    | ent       | V <sub>I</sub> = 0                                                                           |                       |      | -10                    |     |       | -10  | μΑ     |

|                 | Output leakage                                          | OUT1      | DB0-DB7 at 0 V, $\overline{WR}$ , $\overline{CS}$ at 0 V, $V_{ref} = \pm 10 \text{ V}$       |                       |      | ±400                   |     |       | ±200 | nA     |

| likg            | current                                                 | OUT2      | DB0-DB7 at $V_{DD}$ , $\overline{WR}$ , $\overline{CS}$ at 0 V, $V_{ref} = \pm 10 \text{ V}$ |                       |      | ±400                   |     |       | ±200 | IIA    |

| la a            | Supply current                                          | Quiescent | DB0-DB7 at V <sub>IH</sub> min or V <sub>IL</sub> max                                        |                       |      | 1                      |     |       | 2    | mA     |

| <sup>1</sup> DD |                                                         | Standby   | DB0-DB7 at 0 V or V <sub>DD</sub>                                                            |                       |      | 500                    |     |       | 500  | μΑ     |

| ksvs            | ksvs Supply voltage sensitivity, Δgain/ΔV <sub>DD</sub> |           | ΔV <sub>DD</sub> = ±10%                                                                      |                       | 0.01 | 0.16                   |     | 0.005 | 0.04 | %FSR/% |

| Ci              | C <sub>i</sub> Input capacitance, DB0–DB7, WR, CS       |           | V <sub>I</sub> = 0                                                                           |                       |      | 5                      |     |       | 5    | pF     |

|                 | OUT1                                                    |           |                                                                                              | 30                    |      |                        | 30  |       |      |        |

|                 | Output                                                  | OUT2      | DB0–DB7 at 0 V, WR, CS at 0 V                                                                |                       |      | 120                    |     |       | 120  | pF     |

| Co              | capacitance                                             | OUT1      | DB0-DB7 at V <sub>DD</sub> , WR, CS at 0 V                                                   |                       |      | 120                    |     |       | 120  | ρг     |

|                 |                                                         | OUT2      | DB0–DB7 at $V_{DD}$ , $\overline{WR}$ , $\overline{CS}$ at 0 V                               |                       |      | 30                     |     |       | 30   |        |

|                 | Reference input impedance (REF to GND)                  |           |                                                                                              | 5                     |      | 20                     | 5   |       | 20   | kΩ     |

# TLC7524C, TLC7524E, TLC7524I 8-BIT MULTIPLYING DIGITAL-TO-ANALOG CONVERTERS

SLAS061A - SEPTEMBER 1986 - REVISED MARCH 1995

# operating characteristics over recommended operating free-air temperature range, $V_{ref}$ = $\pm 10$ V, OUT1 and OUT2 at GND (unless otherwise noted)

| DADAMETED                                                                  | TEST COMPITIONS                                                                                                                                              | ۷ <sub>l</sub> | V <sub>DD</sub> = 5 V |         | V <sub>DD</sub> = 15 V |                  |      |      |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|---------|------------------------|------------------|------|------|

| PARAMETER                                                                  | PARAMETER TEST CONDITIONS                                                                                                                                    |                | TYP                   | MAX     | MIN                    | TYP <sup>†</sup> | MAX  | UNIT |

| Linearity error                                                            |                                                                                                                                                              |                |                       | ±0.5    |                        |                  | ±0.5 | LSB  |

| Gain error                                                                 | See Note 1                                                                                                                                                   |                |                       | ±2.5    |                        |                  | ±2.5 | LSB  |

| Settling time (to 1/2 LSB)                                                 | See Note 2                                                                                                                                                   |                |                       | 100     |                        |                  | 100  | ns   |

| Propagation delay from digital input to 90% of final analog output current | See Note 2                                                                                                                                                   |                |                       | 80      |                        |                  | 80   | ns   |

| Feedthrough at OUT1 or OUT2                                                | $\frac{\text{Vref}}{\text{WR}} = \pm 10 \text{ V} \text{ (100-kHz sinewave)}$<br>$\frac{\text{VR}}{\text{WR}} = \pm 10 \text{ V} \text{ (100-kHz sinewave)}$ |                |                       | 0.5     |                        |                  | 0.5  | %FSR |

| Temperature coefficient of gain                                            | $T_A = 25^{\circ}C$ to MAX                                                                                                                                   | ±0.004 ±0.001  |                       | %FSR/°C |                        |                  |      |      |

NOTES: 1. Gain error is measured using the internal feedback resistor. Nominal full scale range (FSR) = V<sub>ref</sub> - 1 LSB.

OUT1 load = 100 Ω, C<sub>ext</sub> = 13 pF, WR at 0 V, CS at 0 V, DB0-DB7 at 0 V to V<sub>DD</sub> or V<sub>DD</sub> to 0 V.

### operating sequence

SLAS061A - SEPTEMBER 1986 - REVISED MARCH 1995

### **APPLICATION INFORMATION**

### voltage-mode operation

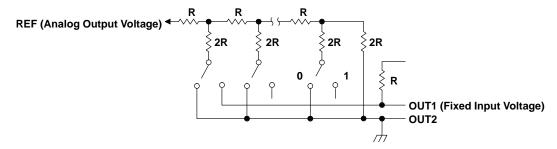

It is possible to operate the current-multiplying DAC in these devices in a voltage mode. In the voltage mode, a fixed voltage is placed on the current output terminal. The analog output voltage is then available at the reference voltage terminal. Figure 1 is an example of a current-multiplying DAC, which is operated in voltage mode.

**Figure 1. Voltage Mode Operation**

The relationship between the fixed-input voltage and the analog-output voltage is given by the following equation:

$$V_O = V_I (D/256)$$

where

V<sub>O</sub> = analog output voltage

V<sub>I</sub> = fixed input voltage

D = digital input code converted to decimal

In voltage-mode operation, these devices meet the following specification:

| PARAMETER              | TEST CONDITIONS                                                                | MIN MAX | UNIT |

|------------------------|--------------------------------------------------------------------------------|---------|------|

| Linearity error at REF | $V_{DD} = 5 \text{ V}$ , OUT1 = 2.5 V, OUT2 at GND, $T_A = 25^{\circ}\text{C}$ | 1       | LSB  |

### PRINCIPLES OF OPERATION

The TLC7524C, TLC7524E, and TLC7524I are 8-bit multiplying DACs consisting of an inverted R-2R ladder, analog switches, and data input latches. Binary-weighted currents are switched between the OUT1 and OUT2 bus lines, thus maintaining a constant current in each ladder leg independent of the switch state. The high-order bits are decoded. These decoded bits, through a modification in the R-2R ladder, control three equally-weighted current sources. Most applications only require the addition of an external operational amplifier and a voltage reference.

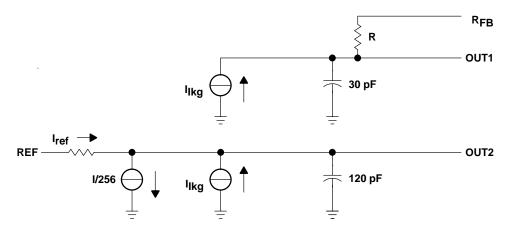

The equivalent circuit for all digital inputs low is seen in Figure 2. With all digital inputs low, the entire reference current, I<sub>ref</sub>, is switched to OUT2. The current source I/256 represents the constant current flowing through the termination resistor of the R-2R ladder, while the current source I<sub>Ikg</sub> represents leakage currents to the substrate. The capacitances appearing at OUT1 and OUT2 are dependent upon the digital input code. With all digital inputs high, the off-state switch capacitance (30 pF maximum) appears at OUT2 and the on-state switch capacitance (120 pF maximum) appears at OUT1. With all digital inputs low, the situation is reversed as shown in Figure 2. Analysis of the circuit for all digital inputs high is similar to Figure 2; however, in this case, I<sub>ref</sub> would be switched to OUT1.

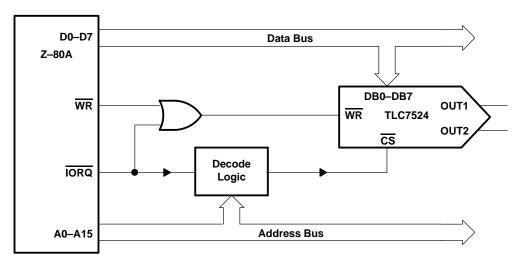

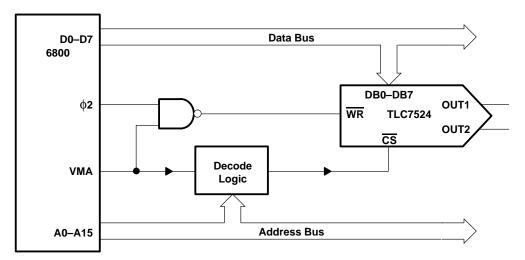

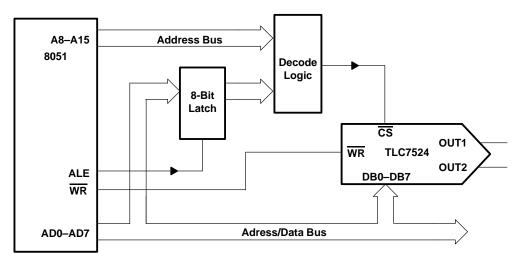

The DAC on these devices interfaces to a microprocessor through the data bus and the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  control signals. When  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  are both low, analog output on these devices responds to the data activity on the DB0–DB7 data bus inputs. In this mode, the input latches are transparent and input data directly affects the analog output. When either the  $\overline{\text{CS}}$  signal or  $\overline{\text{WR}}$  signal goes high, the data on the DB0–DB7 inputs are latched until the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  signals go low again. When  $\overline{\text{CS}}$  is high, the data inputs are disabled regardless of the state of the  $\overline{\text{WR}}$  signal.

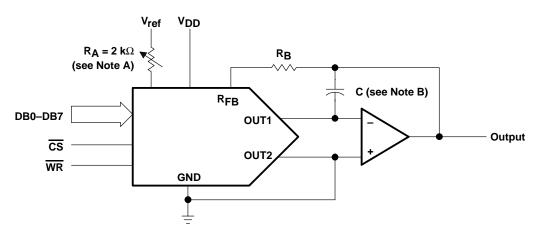

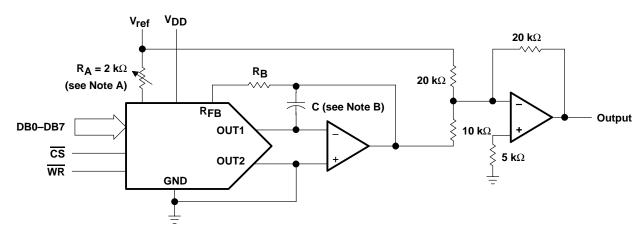

These devices are capable of performing 2-quadrant or full 4-quadrant multiplication. Circuit configurations for 2-quadrant or 4-quadrant multiplication are shown in Figures 3 and 4. Tables 1 and 2 summarize input coding for unipolar and bipolar operation respectively.

Figure 2. TLC7524 Equivalent Circuit With All Digital Inputs Low

### PRINCIPLES OF OPERATION

Figure 3. Unipolar Operation (2-Quadrant Multiplication)

Figure 4. Bipolar Operation (4-Quadrant Operation)

NOTES: A. RA and RB used only if gain adjustment is required.

B. C phase compensation (10-15 pF) is required when using high-speed amplifiers to prevent ringing or oscillation.

**Table 1. Unipolar Binary Code**

| DIGITAL INPUT<br>(see Note 3) |      | ANALOG OUTPUT                        |

|-------------------------------|------|--------------------------------------|

| MSB                           | LSB  |                                      |

| 1111                          | 1111 | -V <sub>ref</sub> (255/256)          |

| 1000                          | 0001 | -V <sub>ref</sub> (129/256)          |

| 1000                          | 0000 | $-V_{ref}$ (128/256) = $-V_{ref}$ /2 |

| 0111                          | 1111 | -V <sub>ref</sub> (127/256)          |

| 0000                          | 0001 | -V <sub>ref</sub> (1/256)            |

| 0000                          | 0000 | 0                                    |

Table 2. Bipolar (Offset Binary) Code

| DIGITAL<br>(see N |      | ANALOG OUTPUT               |

|-------------------|------|-----------------------------|

| MSB               | LSB  |                             |

| 1111              | 1111 | V <sub>ref</sub> (127/128)  |

| 1000              | 0001 | V <sub>ref</sub> (1/128)    |

| 1000              | 0000 | 0                           |

| 0111              | 1111 | -V <sub>ref</sub> (1/128)   |

| 0000              | 0001 | -V <sub>ref</sub> (127/128) |

| 0000              | 0000 | -V <sub>ref</sub>           |

NOTES: 3. LSB =  $1/256 (V_{ref})$

4. LSB =  $1/128 (V_{ref})$

### PRINCIPLES OF OPERATION

## microprocessor interfaces

Figure 5. TLC7524 - Z-80A Interface

Figure 6. TLC7524 - 6800 Interface

# microprocessor interfaces (continued)

Figure 7. TLC7524 - 8051 Interface

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1995, Texas Instruments Incorporated